Peter Fletcher

May 1993

A thesis submitted for the degree of Doctor of Philosophy of The Australian National University

Regular Mapping of Multi-Dimensional Data on Parallel Processors

Peter Fletchar

May 1993

Thesis submitted for the degree of Doctor of Publicophy of The Australian National University

# Declaration

I hereby declare that except where otherwise explicitly stated, the work presented in this thesis is my own original work.

for faller.

Peter Fletcher

Richard Newle, 1921 William, MikeShairan Distanting the second stores and the first stores and the stores and the stores which have above the three states and Steve Woods. Thanks to those who have above me that them is a life outside the com-Danks to those who have above me that them is a life outside the com-Danks to those who have above me that them is a life outside the computer: Heles, Cathorine, Sen. Graham, and the Boys, Sally Kneebook, Dankis, Broos, Kathy and Jamie, Chris and Nikte, Mogga and Phil, Steve and Kiraty, Vorena and Alex, Ouv and Nathalie (andeax and flock, Matture and Koren

Finally, thanks to Marcia and Broosen illy their love and furbrationed, which gave no the freedom to work with collowment.

# Acknowledgements

Firstly many thanks to my supervisor, Phil Robertson, who provided me an opportunity to work in this area, convinced me of its importance, encouraged me to experiment and provided me with substantial feedback from his tireless reviewing of my drafts.

Special thanks to Guy Vézina, whose collaboration and friendship provided me with a great deal of enjoyment and motivation for this work, and whose software is responsible for many of the pretty pictures. Grateful thanks also to Ken Tsui for carefully reviewing the penultimate draft, finding many errors and omissions and assisting me in clarifying many dodgy areas.

Special thanks to people with whom I have had many valuable and stimulating discussions: Dave Abel, Don Bone, Oscar Bosman, Lisa de Ferrari, David Keightley, John Lilleyman, Scott Milton, Jonathon M<sup>c</sup>Cabe, Chris Moran, Heinz Schmidt, Kevin Smith, Duncan Stevenson, Ken Tsui and Andrew Vincent.

Thanks also to Don Fraser and Heiko Schröeder who provided me with useful discussions and material at the start of my thesis; to John O'Callaghan who, in conjunction with the CSIRO, partially supported my work; to the members of my committee: Richard Brent, Iain Macleod and E. Krishnamurthy; to Tom Blank, Jeff Fier, Christopher Glaeser, Larry Levine and Russ Tuck who have helped me understand the MasPar; to Faye Baxendell who has helped me track down many an item; to Mike Sharrot for his help in producing videos; and to Peter Lamb who showed me how to produce postscript output anywhere.

Many people deserve thanks who have made my working environment a rich and enjoyable one: Stephen Barass, Arch Brayshaw, Dave Campbell, David Cook, Trish Devine, Kerry Doutch, Peter Fox, Neale Fulton, Matthew Hutchins, Stuart Hungerford, Fei Jin, Steve Jones, Peter Milne, Kevin Moore, Richard Neville, Peter Nikitser, Mike Sharrot, Dione Smith (for the Strepsils too!), Roy Stockman, Paul Veldkamp, Kathy Visintin, Graham Williams and Steve Woods.

Thanks to those who have shown me that there is a life outside the computer: Helen, Catherine, Ben, Graham, and the Boys, Sally Kneebone, Dennis, Bruce, Kathy and Jamie, Chris and Nikki, Megan and Phil, Steve and Kirsty, Verena and Alex, Guy and Nathalie, Lindsay and Rod, Markus and Karen, Nicola and William, everyone at Aikido, and Chika, Sallie, Judy, Leigh, Graham, Tim, Peter and Carl at Boyce street.

Finally, thanks to Marcia and Bronwen for their love and forbearance, which gave me the freedom to work with enjoyment.

# Abstract

This thesis presents a generalized framework for the mapping and remapping of large regularly-gridded multidimensional data sets on a parallel computer. We address two problems that influence the efficiency with which parallel computers can be exploited in image processing, visualization and simulation applications. The *data mapping problem* is the task of describing the layout of multi-dimensional data set on a parallel array. This layout has a significant effect on the choice and efficiency of processing algorithms. The *data remapping problem* is the task of moving data dynamically between data mappings to provide portability between applications, libraries and external devices, and allows the description of a class of data transformations of use in a variety of data processing algorithms.

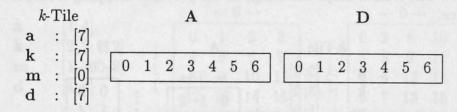

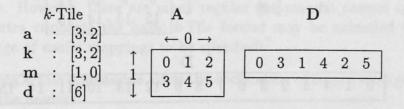

We develop the k-Tile format, which provides a concise and flexible data mapping description for multidimensional data arrays on multidimensional devices, and allows the specification of many commonly used parallel data mappings, geometric transformations of these mappings, data replication and data padding.

Using the k-Tile format we define Parallel mapping functions (PMFs), which provide a general system for performing many remapping tasks. We introduce efficient algorithms for performing a subset of PMFs on a crossbarconnected parallel processing array with indirect addressing, and demonstrate an efficient implementation of these algorithms on a MasPar MP-1 computer. We also explore the problems involved in producing a complete implementation of PMFs on the MasPar, and suggest further work needed to produce such a system.

We show examples of the use of the k-Tile format and PMFs for the data mapping directives of High Performance Fortran, in image processing algorithms and in visualization applications.

# Contents

| 1 | Intr | oducti                | on 1                                                                  |  |  |  |  |

|---|------|-----------------------|-----------------------------------------------------------------------|--|--|--|--|

|   | 1.1  | Multidimensional data |                                                                       |  |  |  |  |

|   | 1.2  | Paralle               | el Architectures                                                      |  |  |  |  |

|   | 1.3  | A fran                | nework for data mapping 2                                             |  |  |  |  |

|   |      | 1.3.1                 | Storage and access requirements                                       |  |  |  |  |

|   |      | 1.3.2                 | Algorithm requirements 3                                              |  |  |  |  |

|   |      | 1.3.3                 | Portability requirements                                              |  |  |  |  |

|   |      | 1.3.4                 | A framework for data mapping 4                                        |  |  |  |  |

|   | 1.4  | The st                | ructure of this thesis                                                |  |  |  |  |

|   |      | 1.4.1                 | Current approaches to data mapping 4                                  |  |  |  |  |

|   |      | 1.4.2                 | The k-Tile format                                                     |  |  |  |  |

|   |      | 1.4.3                 | Radix 2 remapping                                                     |  |  |  |  |

|   |      | 1.4.4                 | Implementation of radix 2 PMFs 5                                      |  |  |  |  |

|   |      | 1.4.5                 | Mixed radix remapping 5                                               |  |  |  |  |

|   |      | 1.4.6                 | The scope of PMFs                                                     |  |  |  |  |

| • | 1.5  | 1 1.                  | ensional spaces, devices and data mapping techniques 7                |  |  |  |  |

| 2 |      |                       | choionaí spaces, acticos ana auta mapping como que                    |  |  |  |  |

|   | 2.1  |                       |                                                                       |  |  |  |  |

|   |      | 2.1.1                 | Multiumonoronal artajo v v v v v v v v v v v v                        |  |  |  |  |

|   |      | 2.1.2                 | Data and index mappings    10      Multidimensional data arrays    12 |  |  |  |  |

|   |      | 2.1.3                 |                                                                       |  |  |  |  |

|   | ~ ~  | 2.1.4                 | Multidimensional devices                                              |  |  |  |  |

|   | 2.2  |                       | mapping on one-dimensional devices                                    |  |  |  |  |

|   |      | 2.2.1                 | The Multidimensional Tile Format                                      |  |  |  |  |

|   |      | 2.2.2                 | Remapping algorithms and applications                                 |  |  |  |  |

|   |      | 2.2.3                 | Hardware approaches to data mapping                                   |  |  |  |  |

|   | 2.3  |                       | el architectures                                                      |  |  |  |  |

|   |      | 2.3.1                 | Properties of Parallel Architectures                                  |  |  |  |  |

|   |      | 2.3.2                 | Three SIMD architectures                                              |  |  |  |  |

|   |      | 2.3.3                 | The MasPar and parallel programming in MPL 24                         |  |  |  |  |

|   | 2.4  |                       | nt data mapping systems                                               |  |  |  |  |

|   |      | 2.4.1                 | Direct permutation                                                    |  |  |  |  |

|   |      | 2.4.2                 | Dimension mapping                                                     |  |  |  |  |

Acknowledgements StrangbelwondoA

|   |     | 2.4.3 Data index computations          | 34 |

|---|-----|----------------------------------------|----|

|   |     | 2.4.4 Index bit maps                   | 35 |

|   |     | 2.4.5 Index digit maps                 | 35 |

|   |     | 2.4.6 Blip schemes                     | 36 |

|   |     | 0.47 $11$ 1                            | 36 |

|   |     |                                        | 37 |

|   | 2.5 | C                                      | 38 |

| 3 | Th  | e k-Tile format                        | 41 |

|   | 3.1 | The Basic k-Tile Format                | 42 |

|   |     |                                        | 42 |

|   |     |                                        | 42 |

|   |     |                                        | 43 |

|   |     |                                        | 44 |

|   |     |                                        | 44 |

|   |     |                                        | 44 |

|   |     |                                        | 46 |

|   |     |                                        | 48 |

|   |     |                                        | 49 |

|   |     |                                        | 49 |

|   |     |                                        | 50 |

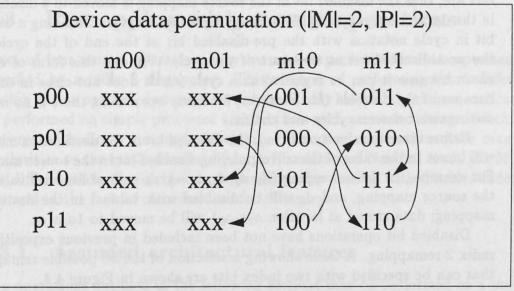

|   |     |                                        | 51 |

|   | 3.2 |                                        | 53 |

|   |     |                                        | 54 |

|   |     |                                        | 55 |

|   |     |                                        | 56 |

|   |     |                                        | 59 |

|   |     |                                        | 63 |

|   |     |                                        | 65 |

|   | 3.3 |                                        | 67 |

|   | 3.4 |                                        | 67 |

| 4 | Rac | lix 2 remapping                        | 69 |

|   | 4.1 |                                        | 69 |

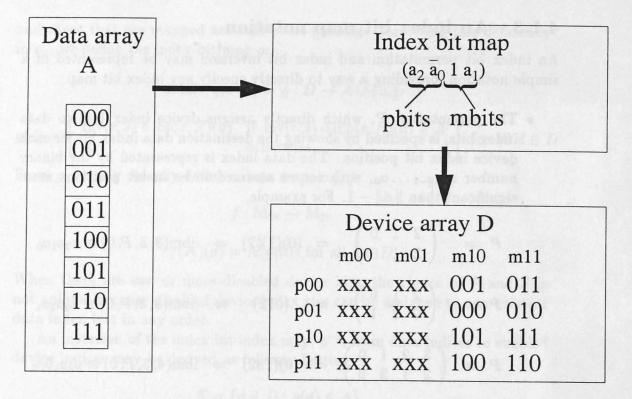

|   |     | 4.1.1 An overview of the index bit map | 70 |

|   |     | 4.1.2 Definition of the index bit map  | 73 |

|   |     | 4.1.3 An index bit map notation        | 79 |

|   | 4.2 | D 11 0 .                               | 79 |

|   |     |                                        | 81 |

|   |     | 4.2.2 A radix 2 remapping notation     | 82 |

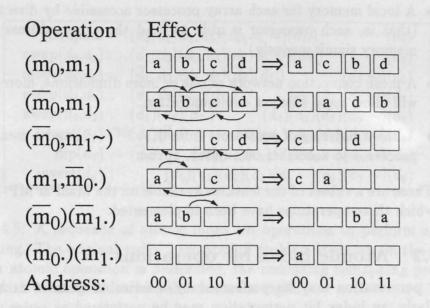

|   | 4.3 | Remapping with atomic operations       | 35 |

|   |     |                                        | 85 |

|   |     | 4.3.2 Atomic index bit operations      | 36 |

v

### CONTENTS

|   |     | 4.3.3                               | Efficient use of atomic index bit operations                                                    |  |  |  |  |

|---|-----|-------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

|   | 4.4 |                                     | al radix 2 remapping                                                                            |  |  |  |  |

|   |     | 4.4.1                               | Assumed architectural features                                                                  |  |  |  |  |

|   |     | 4.4.2                               | Types of cycles                                                                                 |  |  |  |  |

|   |     | 4.4.3                               | A recursive approach                                                                            |  |  |  |  |

|   |     | 4.4.4                               | (p*) cycles                                                                                     |  |  |  |  |

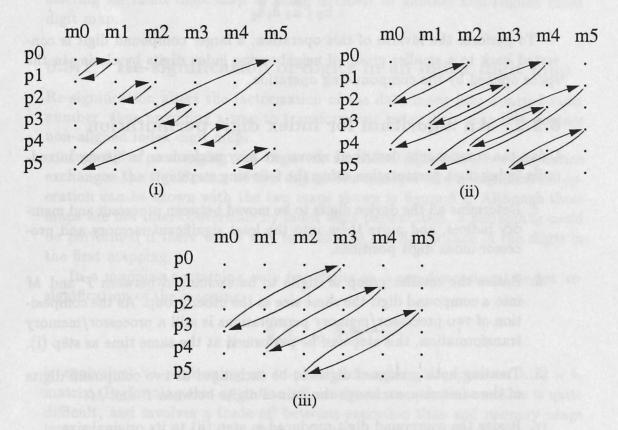

|   |     | 4.4.5                               | $(m*)$ cycles $\ldots \ldots 91$ |  |  |  |  |

|   |     | 4.4.6                               | Simultaneous $(m*)$ and $(p*)$ cycles $\ldots \ldots \ldots 95$                                 |  |  |  |  |

|   |     | 4.4.7                               | Transforming mixed cycles into $(mp*)$ cycles 95                                                |  |  |  |  |

|   |     | 4.4.8                               | Even-parity $(mp*)$ cycles                                                                      |  |  |  |  |

|   |     | 4.4.9                               | Identity cycles                                                                                 |  |  |  |  |

|   |     | 4.4.10                              | Remapping data while copying                                                                    |  |  |  |  |

|   | 4.5 | Summa                               | ary                                                                                             |  |  |  |  |

| 5 | Imp | lement                              | ation of Radix 2 PMFs 105                                                                       |  |  |  |  |

|   | 5.1 |                                     | -Tile format                                                                                    |  |  |  |  |

|   |     |                                     | Converting a $2^k$ -Tile format to an index bit map 106                                         |  |  |  |  |

|   |     | 5.1.2                               | A canonical form of the $2^k$ -Tile format                                                      |  |  |  |  |

|   |     | 5.2 Data types used by radix 2 PMFs |                                                                                                 |  |  |  |  |

|   | 5.3 |                                     | ons used to access PMFs                                                                         |  |  |  |  |

|   |     | 5.3.1                               | k-Tile format manipulation                                                                      |  |  |  |  |

|   |     | 5.3.2                               | mtag manipulation                                                                               |  |  |  |  |

|   |     | 5.3.3                               | 11 0                                                                                            |  |  |  |  |

|   |     | 5.3.4                               |                                                                                                 |  |  |  |  |

|   |     | 5.3.5                               | Geometrical transformations                                                                     |  |  |  |  |

|   | 5.4 |                                     | ure of the PMF system                                                                           |  |  |  |  |

|   | 5.5 | -                                   |                                                                                                 |  |  |  |  |

|   | 5.6 |                                     | using the optimal algorithm                                                                     |  |  |  |  |

|   |     | 5.6.1                               |                                                                                                 |  |  |  |  |

|   |     |                                     | PE register usage                                                                               |  |  |  |  |

|   |     | 5.6.3                               | Chunking to larger data objects                                                                 |  |  |  |  |

|   |     | 5.6.4                               | Processor cluster optimizations                                                                 |  |  |  |  |

|   |     | 5.6.5                               | Using the xnet for $P/M$ transpositions                                                         |  |  |  |  |

|   | 5.7 |                                     | g                                                                                               |  |  |  |  |

|   |     | 5.7.1                               | Generation of random remappings                                                                 |  |  |  |  |

|   |     | 5.7.2                               | Checking performed remappings                                                                   |  |  |  |  |

|   |     | 5.7.3                               | Results of testing                                                                              |  |  |  |  |

|   |     | 5.7.4                               | A non-assembler library                                                                         |  |  |  |  |

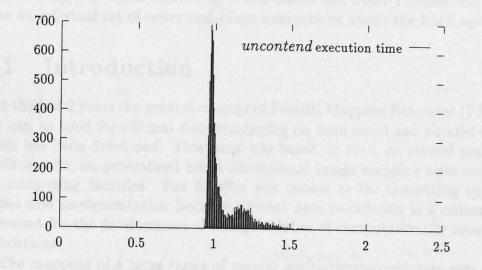

|   | 5.8 |                                     | 121                                                                                             |  |  |  |  |

|   |     | 5.8.1                               | Execution time of radix 2 remapping                                                             |  |  |  |  |

|   |     | 5.8.2                               | Hand coding vs. PMFs                                                                            |  |  |  |  |

|   | 5.9 | Summ                                | nary                                                                                            |  |  |  |  |

vi

### CONTENTS

| 6 | Mix | ed rad | lix remapping                                    | 133 |

|---|-----|--------|--------------------------------------------------|-----|

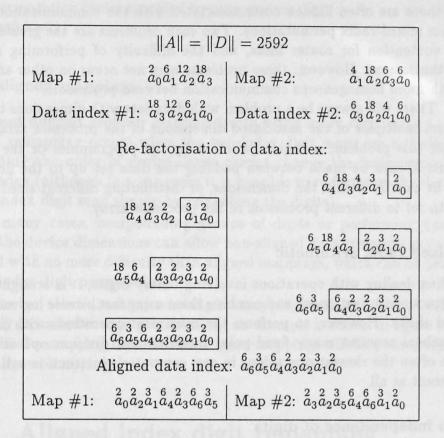

|   | 6.1 | The in | ndex digit map                                   | 133 |

|   |     | 6.1.1  | Mixed radix numbers                              | 133 |

|   |     | 6.1.2  | Indexing with a mixed radix number               |     |

|   |     | 6.1.3  | Specifying an index digit map                    |     |

|   |     | 6.1.4  | Specifying a mixed radix remapping               |     |

|   | 6.2 | Aligne | ed index digit remapping                         | 141 |

|   |     | 6.2.1  | Algorithm components                             |     |

|   |     | 6.2.2  | An algorithm for index digit permutation         |     |

|   | 6.3 | Non-a  | ligned index digit remapping                     | 147 |

|   |     | 6.3.1  | Re-signification of digits in an index digit map |     |

|   |     | 6.3.2  | Re-signification within device dimensions        |     |

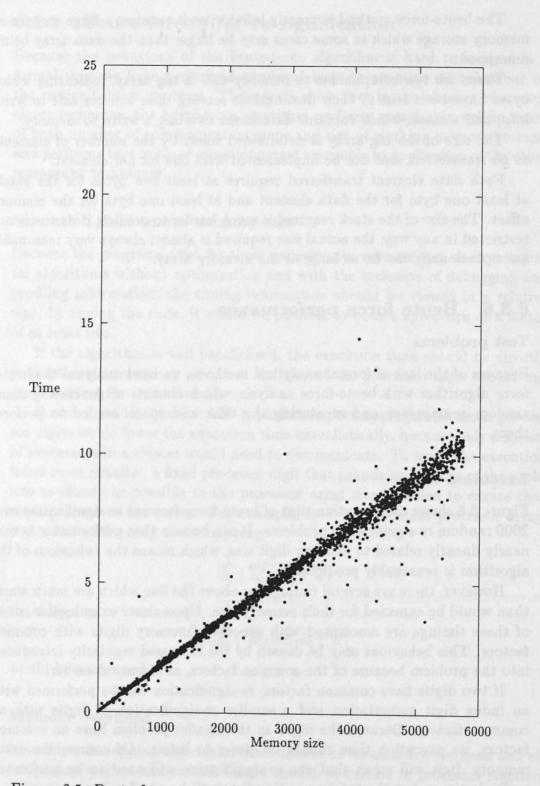

|   |     | 6.3.3  | "Brute force" remapping                          | 150 |

|   |     | 6.3.4  | Re-signification across device dimensions        |     |

|   |     | 6.3.5  | Brute-force $P/M$ re-signification               | 156 |

|   |     | 6.3.6  | Brute force performance                          | 157 |

|   |     | 6.3.7  | Restricting to relatively prime digits           |     |

|   |     | 6.3.8  | Skewing initial memory addresses                 |     |

|   |     | 6.3.9  | Restricting stack size                           | 163 |

|   | 6.4 | Cluste | er contention removal                            | 166 |

|   |     | 6.4.1  | A cluster contention removal algorithm           |     |

|   |     | 6.4.2  | Removing contention in mixed-radix remapping     |     |

|   | 6.5 | A syst | em for mixed radix remapping                     | 171 |

|   | 6.6 | Summ   | ary                                              | 172 |

| 7 | The | scope  | of data mapping operations                       | 175 |

|   | 7.1 | High H | Performance Fortran                              |     |

|   |     | 7.1.1  | ALIGN and REALIGN directives                     | 175 |

|   |     | 7.1.2  | HPF PROCESSORS directive                         | 179 |

|   |     | 7.1.3  | Processor VIEWs                                  | 180 |

|   |     | 7.1.4  | DISTRIBUTE and REDISTRIBUTE directives           | 180 |

|   |     | 7.1.5  | TEMPLATE directive                               | 180 |

|   |     | 7.1.6  | $PMFs \supset HPF$                               | 181 |

|   | 7.2 | KIPS   |                                                  | 181 |

|   | 7.3 | Sampl  | e applications                                   | 182 |

|   |     | 7.3.1  | Scan-line algorithms                             | 182 |

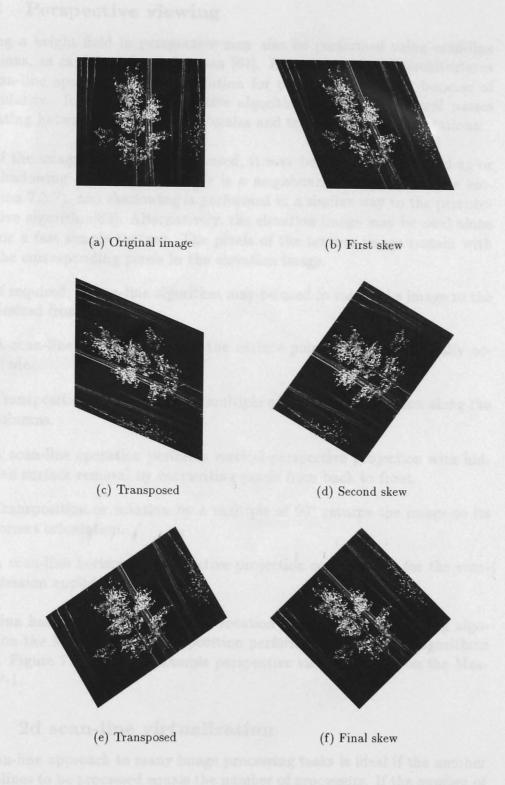

|   |     | 7.3.2  | 2d rotation                                      | 182 |

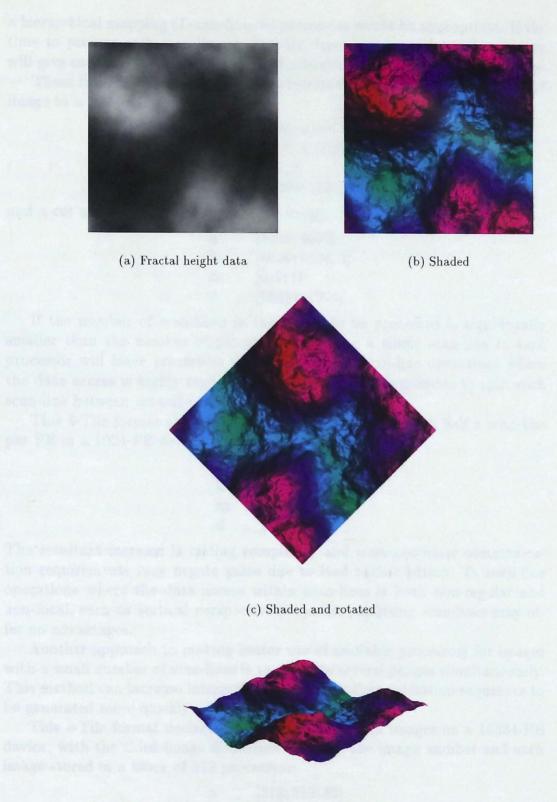

|   |     | 7.3.3  | Perspective viewing                              | 185 |

|   |     | 7.3.4  | 2d scan-line virtualization                      | 185 |

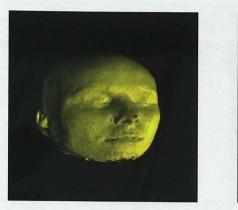

|   |     | 7.3.5  | Volume rotation and rendering                    |     |

|   |     | 7.3.6  | The Fast Fourier Transform                       |     |

|   |     | 7.3.7  | Neighbourhood operations                         |     |

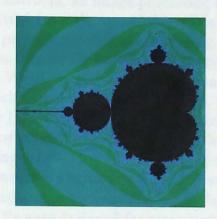

|   |     | 7.3.8  | Computing the Mandelbrot set                     | 196 |

vii

### CONTENTS

|    | 7.4                             | Summary                                                                                                                                                                                                                                                                                                                                        |

|----|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | Con<br>8.1<br>8.2<br>8.3<br>8.4 | clusions201The data mapping problem201The data remapping problem2028.2.1Radix 2 PMFs2028.2.2Mixed radix remapping203Application of the approach203Limitations of the approach, and future work2048.4.1Data structures2048.4.2Data-dependent mappings and operations2048.4.3A general PMF system2058.4.4Human interaction with data mappings205 |

| Bi | bliog                           | raphy 207                                                                                                                                                                                                                                                                                                                                      |

| A  | -                               | ster contention removal 213                                                                                                                                                                                                                                                                                                                    |

| B  | Stat                            | tus of PMFs 221                                                                                                                                                                                                                                                                                                                                |

| -  | B.1                             | Introduction                                                                                                                                                                                                                                                                                                                                   |

|    | B.2                             | PMF system calls                                                                                                                                                                                                                                                                                                                               |

|    |                                 | B.2.1 The k-Tile format                                                                                                                                                                                                                                                                                                                        |

|    |                                 | B.2.2 The mtag                                                                                                                                                                                                                                                                                                                                 |

|    |                                 | B.2.3 The remap                                                                                                                                                                                                                                                                                                                                |

|    |                                 | B.2.4Standard mappings229B.2.5Geometrical transformations231                                                                                                                                                                                                                                                                                   |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                |

|    | B.3                             | Examples of Using PMFs                                                                                                                                                                                                                                                                                                                         |

|    |                                 | B.3.1 Performing a simple remap                                                                                                                                                                                                                                                                                                                |

|    |                                 | B.3.2 Error reporting                                                                                                                                                                                                                                                                                                                          |

|    |                                 | B.3.3 Fourier transform                                                                                                                                                                                                                                                                                                                        |

|    |                                 | B.3.4 Mandelbrot set generator                                                                                                                                                                                                                                                                                                                 |

|    | B.4                             | Some header files                                                                                                                                                                                                                                                                                                                              |

|    |                                 | B.4.1 gr.h                                                                                                                                                                                                                                                                                                                                     |

|    |                                 | B.4.2 Extract from gp2.h                                                                                                                                                                                                                                                                                                                       |

|    | B.5                             | PMF Implementation notes                                                                                                                                                                                                                                                                                                                       |

|    | B.6                             | Using the PMF workbench                                                                                                                                                                                                                                                                                                                        |

|    |                                 | B.6.1 Declaring a k-Tile format $\dots \dots \dots$                                                                                                                                                                                            |

|    |                                 | B.6.2 The kmap                                                                                                                                                                                                                                                                                                                                 |

|    |                                 | B.6.3 Declaring an mtag                                                                                                                                                                                                                                                                                                                        |

|    |                                 | B.6.4 Declaring a pair                                                                                                                                                                                                                                                                                                                         |

|    |                                 | B.6.5 Data types attached to a pair                                                                                                                                                                                                                                                                                                            |

|    |                                 | B.6.6 Performing a remap                                                                                                                                                                                                                                                                                                                       |

|    |                                 | B.6.7 Timing                                                                                                                                                                                                                                                                                                                                   |

|    |                                 |                                                                                                                                                                                                                                                                                                                                                |

C Glossary of symbols

viii

261

# List of Figures

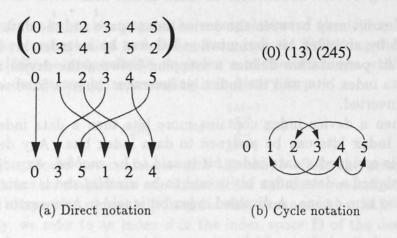

| 4.1  | Representing a permutation in direct and cycle notation 74          |

|------|---------------------------------------------------------------------|

| 4.2  | An example index bit map                                            |

| 4.3  | An example radix 2 remapping 83                                     |

| 4.4  | Example remappings on index bits                                    |

| 4.5  | Example atomic operations for a radix 2 remapping 87                |

| 4.6  | A memory permutation as a linked list                               |

| 4.7  | Transformation of mixed cycle into $(m*)$ and $(mp*)$ cycles 97     |

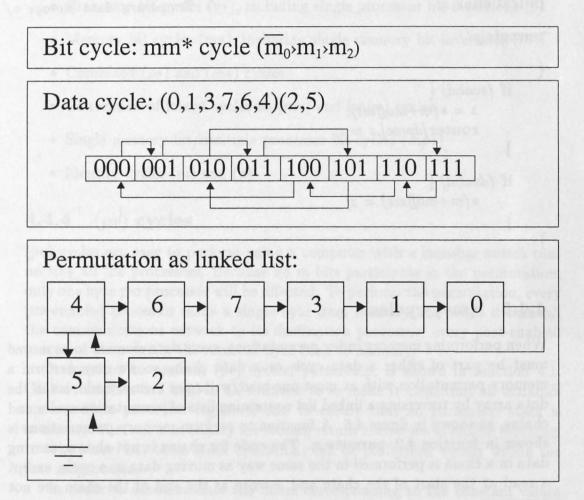

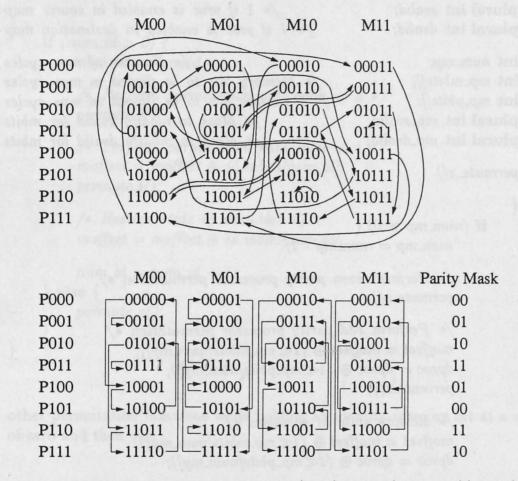

| 4.8  | Parity masking to align $(mp*)$ cycles                              |

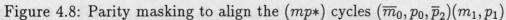

| 5.1  | Partial structure of a PMF implementation                           |

| 5.2  | Base time for MasPar instructions                                   |

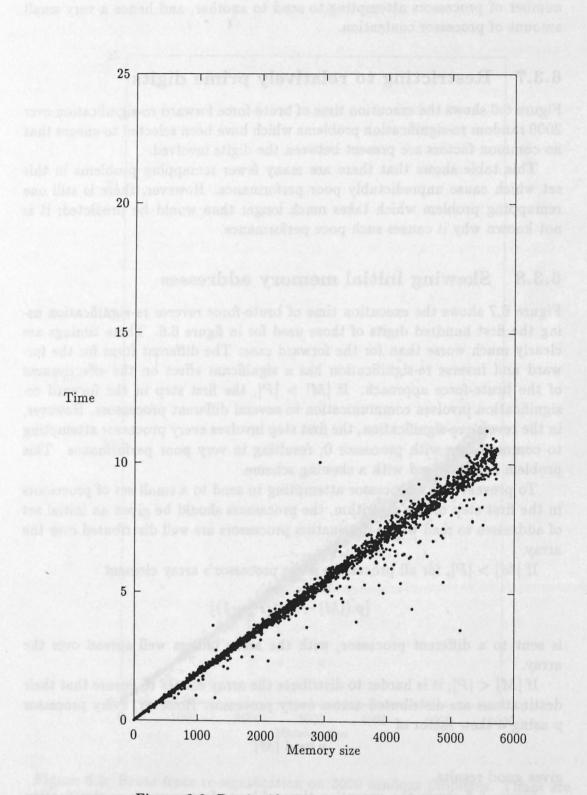

| 5.3  | Execution time of radix 2 PMFs                                      |

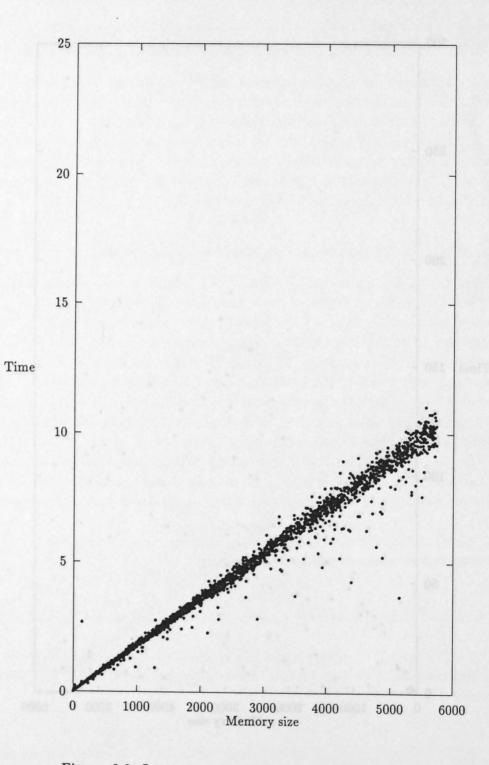

| 5.4  | Lower bound time of radix 2 PMFs                                    |

| 5.5  | PMFs vs. mpipl for $512 \times 512$ image                           |

| 5.6  | PMFs vs. mpipl for $1024 \times 1024$ image                         |

| 5.7  | PMFs vs. mpipl for $2048 \times 2048$ image                         |

| 5.8  | PMFs vs. mpipl for $512 \times 2048$ image                          |

| 61   | Aligning two index digit many                                       |

| 6.1  | Aligning two index digit maps                                       |

| 6.2  | Non-alignable index digit maps                                      |

| 6.3  | P/M digit exchange                                                  |

| 6.4  | Re-signification within device dimensions                           |

| 6.5  | Brute-force re-signification                                        |

| 6.6  | Brute-force re-signification without common factors 160             |

| 6.7  | Inverse re-signification                                            |

| 6.8  | Inverse re-signification with address skewing                       |

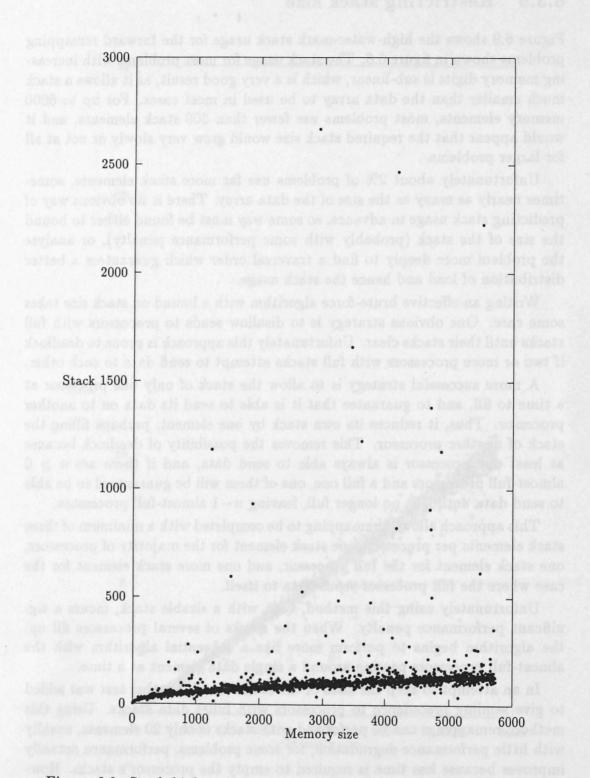

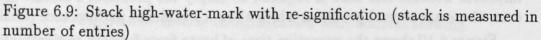

| 6.9  | Re-signification stack high-water-mark                              |

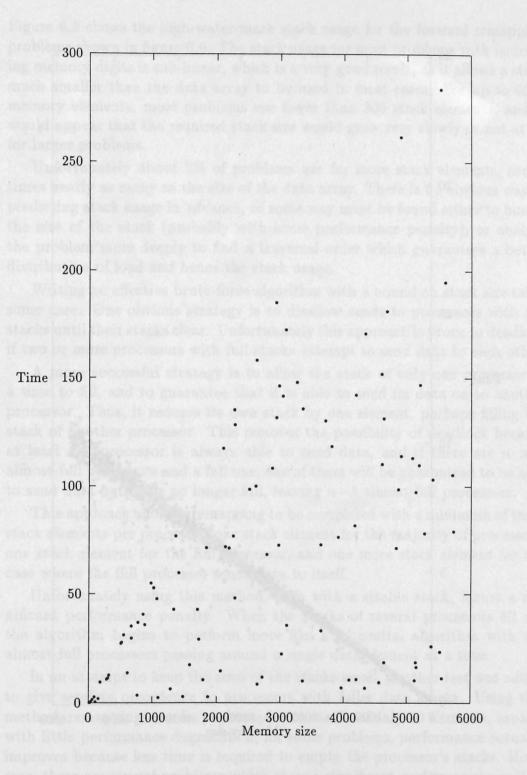

|      | Re-signification execution time with bounded stack                  |

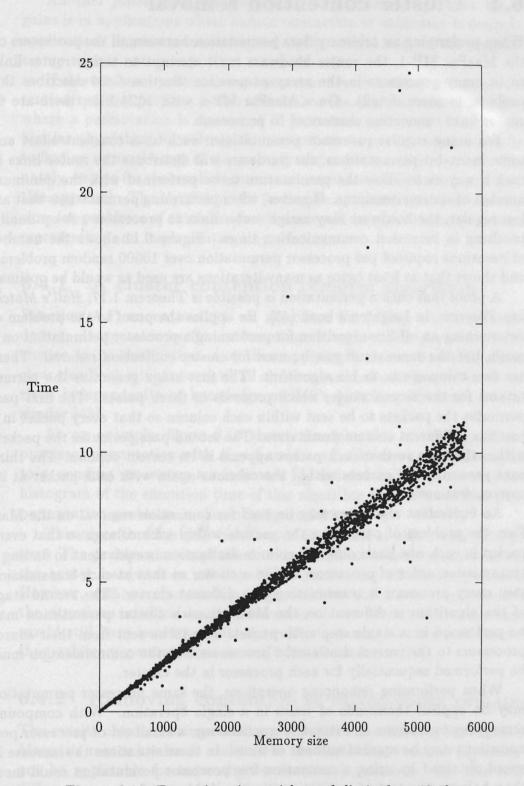

|      | Router iterations required for random permutations                  |

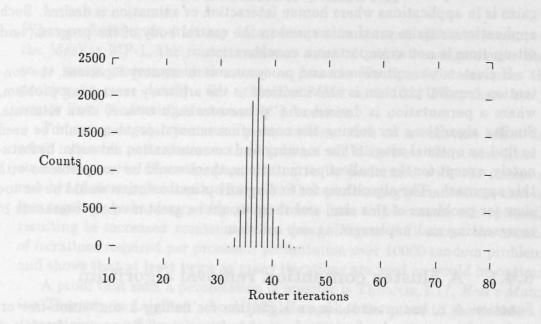

|      | Router iterations required for index digit swaps                    |

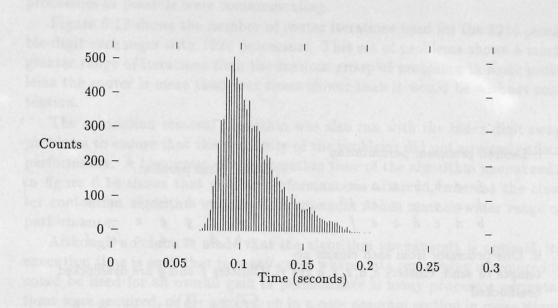

|      | Contention removal time for random problems                         |

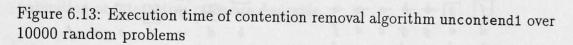

|      | Contention removal time for index digit swap problems 169           |

| 6.15 | Finding a contention-free ordering of a processor permutation . 170 |

### LIST OF FIGURES

| 7.1 | Operations to rotate an image $45^{\circ}$                          |

|-----|---------------------------------------------------------------------|

| 7.2 | Perspective images generated on the MasPar MP-1                     |

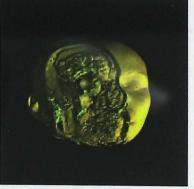

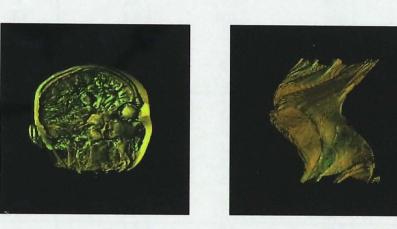

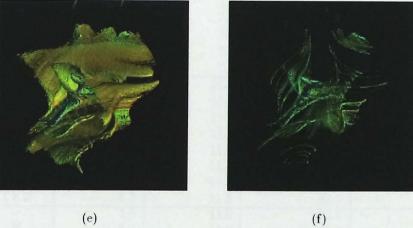

| 7.3 | Volume renderings of human head and strange attractor 190           |

| 7.4 | Volume remapping times for 1K PE MasPar                             |

| 7.5 | Volume remapping times for 8K PE MasPar                             |

| 7.6 | Comparison of Mandelbrot set calculation times                      |

|     | Test sections of the Mandelbrot set                                 |

|     | Finding a contention-free ordering of a processor permutation . 214 |

| A.2 | Execution time of scrambling contention removal                     |

х

# Chapter 1

# Introduction

With the profusion of data being gathered, generated and processed today, more powerful computers and faster computational techniques are becoming essential. Because of physical constraints on the speed of electronic devices, significantly faster performance may only be obtained by pipelining or parallelizing computation.

Ultimately, this data must be presented in a form suitable for interpretation by a person. Many stages of processing may be required to present this data in a meaningful way, entailing the movement of data between and within storage, display and computational devices to allow various transformations to be applied.

The method used for assigning storage locations to data on any of these devices can have a significant effect on the efficiency of large-scale operations on data; we call this task the *data mapping problem*. Once storage locations have been assigned to data, it may be necessary to re-order the data on the device; we call this task the *data remapping problem*.

This thesis provides justification for exploring these two problems, and presents a framework for specifying and manipulating mappings of large regularly gridded data sets on parallel processors.

# 1.1 Multidimensional data

Large data sets can be generated from a variety of sources: optical scanners, remote satellite sensors, CT scanners, imaging spectrometers, video cameras and simulations are but a few. As sensor technology and computational power improve, the size of multidimensional data sets is growing rapidly.

Each type of data has associated with it some dimensionality. Spatial data is usually two or three dimensional; two dimensional data sets are commonly produced by remote sensing devices and optical scanners, and three dimensional data sets by CT scanners, MRI or by stacking two dimensional sections. Dimensionality may also be increased by including information sampled along some other axis; for example, including spectral information at every data point may multiply the size of a data set hundreds of times, and sampling the data set temporally for an animation may multiply its size thousands of times again.

Many large data sets are regularly-gridded and rectilinear. By applying transformations to irregularly-gridded data, many data sets may be treated as regularly gridded and rectilinear. This form of data is ideally suitable for processing on a SIMD parallel processor.

### **1.2** Parallel Architectures

Although many of the techniques in this thesis are applicable to any class of computer, the algorithms in this thesis have been developed for a particular class of computer, a massively parallel distributed-memory SIMD computer. Machines of this class share a number of features which allow efficient algorithms to be found for many problems involving regular operations on a large dataset. These machines have many architectural variations which have a significant effect on the type of algorithms which can be implemented, and hence their efficiency.

The algorithms developed in this thesis were implemented on the MasPar MP-1. However, many of the ideas to be presented are also applicable to other parallel processors, and the specification techniques are applicable to any computer.

### 1.3 A framework for data mapping

When processing large multidimensional data sets, it is desirable that the computer architecture and software tools used satisfy several requirements: convenient storage and data access; appropriate positioning of the data to allow algorithms to operate efficiently (or efficient algorithms to be used); and portability of data and applications to other architectures with a minimum of decoding or recoding. These three requirements can be met by a suitable framework for data mapping.

### **1.3.1** Storage and access requirements

For fast processing and interaction with data we need to communicate data quickly between and within data source, viewing, bulk storage and processing devices. Dedicated devices such as frame buffers and scanners are often inflexible in their formats for accessing data, and standard data file formats also impose limitations on the order of access of multidimensional data. Many

#### 1.3. A FRAMEWORK FOR DATA MAPPING

processors, and massively parallel SIMD processors in particular, have specific requirements for the format of data storage, both for internal representation and access to data stored externally. Because these requirements are often imposed by system software packages, they cannot be changed to suit an application program's requirements; indeed, if several packages are being used together, their requirements can easily conflict.

To integrate all these devices in a data processing environment, and resolve the possible differences in data access requirements, the data handling problem may be consolidated into a generalized framework. This eases the task of programming data handling and allows compatibility to be provided between different programming efforts.

### **1.3.2** Algorithm requirements

When using a parallel processor to transform multidimensional data, the most convenient mapping of the data onto the processor might not be the most convenient mapping for actually performing the transformation, because different algorithms need to see different parts of the data during their execution. Two examples that illustrate this problem are neighbourhood filters and fast Fourier transforms.

When reading data from disk into a parallel processor the data is often stored simply in scan-line order, which makes it easiest to map scan-lines to processors. Unfortunately, the most efficient way of mapping a two dimensional data set to a processor array for the application of a neighbourhood filter is as a matrix of two dimensional tiles, and for a two dimensional Fourier transform the data may need to be index-digit reversed.

Rather than reading data from the disk in tiled or index-digit-reversed order, either of which is likely to be both slow and complicated (unless the data was originally stored in this order), it would seem more efficient to map the data onto the parallel processor in its natural order, and then use the parallel processor to remap the data using fast parallel techniques.

### **1.3.3** Portability requirements

Although most parallel computers have many features in common, there are several programming languages, data mapping techniques and terminologies for describing essentially the same data mappings.

To make life easier for the programmer, a consistent framework for describing and manipulating multidimensional data is needed to make it possible to both formally specify a convenient data mapping and provide a means to convert the specified mapping into any mapping used by other applications.

As both an aid to development and to enable software to be used on smaller systems, this scheme should not only be available on different parallel architectures, but also for use with sequential machines. In practice, using parallel techniques on sequential machines may have additional advantages, such as locally limiting and regularizing data access to local regions of memory, simplifying algorithms and reducing memory paging [61].

# 1.3.4 A framework for data mapping

A general framework is needed for describing data mappings conveniently in a way that is not constrained to a particular architecture. This framework must be high-level enough that efficient implementations are not restricted to a particular architecture or computing paradigm, and low-level enough that application programmers can participate in choosing data mappings appropriate for their particular problems.

As compiler technology improves these issues will increasingly be hidden from the programmer, but a good underlying model will still be necessary to enable compilers to handle large multidimensional data sets efficiently.

# 1.4 The structure of this thesis

The following paragraphs outline the structure of this thesis and the major focus for each chapter.

# 1.4.1 Current approaches to data mapping

The data mapping problem is not new; several systems for data mapping have been used for more than a decade, and schemes for improving data access efficiency on sequential computers and disk drives have been used for many years before that. Chapter 2 surveys some computer architectures, defines regular data structures more fully, and examines current approaches for data mapping. Limitations of current approaches are described.

### 1.4.2 The k-Tile format

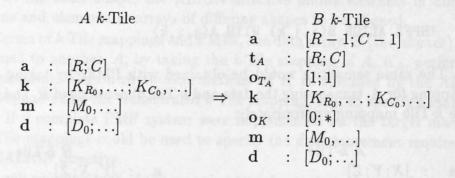

The k-Tile format provides a basis for solutions to the data mapping problem which avoids many of the limitations associated with current approaches. The basic form of the k-Tile format allows many useful data mappings to be described, and extensions to the basic form allow even more flexibility.

Pairs of k-Tile formats may be used to define data remappings. We call this system for specifying remappings *parallel mapping functions* (PMFs). Chapter 3 defines the k-Tile format and PMFs.

4

### 1.4.3 Radix 2 remapping

Although the k-Tile format provides flexibility in specifying data mappings, it does not prescribe any algorithms for performing data remappings using parallel mapping functions. Indeed, it should not; to provide maximum portability, a variety of algorithms are necessary to suit the characteristics of different machine architectures.

Chapter 4 examines algorithms for performing parallel mapping functions based on k-Tile specifications with data-set dimensions restricted in length to powers of two. These operations are performed using the idea of *index* bit permutation [27,28], or radix 2 index digit permutation. A new set of algorithms with optimal communication characteristics is introduced for the MasPar MP-1

### 1.4.4 Implementation of radix 2 PMFs

Chapter 5 describes the implementation and interfacing of the algorithms described in chapter 4 for the MasPar MP-1. Architecture-dependent optimizations have been used to improve the speed of the implementation. Testing and timing results are shown and compared with other data remapping tools, showing that general data remapping algorithms compare favourably with purposebuilt routines.

### 1.4.5 Mixed radix remapping

Although the radix 2 algorithms are efficient and regular, the restriction to powers of two causes a loss of flexibility. Chapter 6 introduces more general algorithms for performing *index digit permutation* and *re-signification*, again suitable for the MasPar MP-1, which may be used for performing remapping operations for general PMFs.

Several problems remain to be addressed in mixed radix remapping, and a mixed radix PMF system is outlined and suggested as future work.

### 1.4.6 The scope of PMFs

Chapter 7 explores the problems to be addressed by PMFs. The relationship between PMFs and the data-mapping directives of High Performance Fortran are examined. PMFs are demonstrated in a range of applications: scan-line algorithms used for affine transformations, surface view generation and volume visualization; neighbourhood operations such as filtering and mathematical morphology; the fast Fourier Transform; and pixel-local operations such as the generation of views of the Mandelbrot set. A there is a the following problem by the support have an example of the second state of the second sta

tor claim particular moments

There is a substantiant of the first of the second state in a second state of the seco

weignamest riber bezild.

Although the option of heading and a second contract and the meridial continues in porters of two causes a true of headbalty. Chapter 6 introduces the contract weathing the period barries are set with a second for and the second second second contracts for the period barries with the second of the second second second second contracts for the period barries with the second of the second second second second contracts for the period barries are set of the second of the second second second contracts for the period barries are set of the second second second second second contracts for the period barries are set of the second of the second second second second contracts for the period barries are set of the second of the second second second second second second second to the second second second second second second second second to be barries are second and the second second second second second second second barries are second and the second barries are second and the second secon

LA.S. I he acops of PMEs

# Chapter 2

# Multidimensional spaces, devices and data mapping techniques

As we have seen in the previous chapter, there is a good case for providing a framework for defining data mappings and algorithms for performing remappings efficiently. There are already many systems and techniques for specifying and manipulating the mapping of multidimensional data for both sequential and parallel computers.

To restrict the scope of this thesis, we will only be dealing with rectangularly gridded multidimensional objects with a fixed number of elements along each dimension. We will not examine irregularly shaped data sets or devices which cannot be made to fit within objects of this type. We will also assume that data mappings are *data-value independent*. These restrictions can increase the data storage required for an arbitrary data set, which in turn can reduce the efficiency of associated algorithms. However, the regularity obtained by these restrictions has many advantages, especially when using parallel architectures.

We will examine two problems associated with multidimensional data sets. When dealing with a multidimensional data set which must be stored in a storage or computation device, some strategy must be used to map the data elements onto the device. This is the data mapping problem referred to in the previous chapter. Once the data has been mapped to the device, we may wish to dynamically alter this mapping by permuting storage locations within the device. This is the data remapping problem referred to in the previous chapter.

## 2.1 Definitions

Before describing data mapping techniques, we describe a notation for multidimensional arrays and mappings.

### 2.1.1 Multidimensional arrays

A multidimensional array is a generalization of a 2d matrix. A matrix generally contains numbers; a multidimensional array may contain any data type. A matrix has only two dimensions, corresponding to rows and columns; a multidimensional array may have any number of dimensions. The number of elements in any row or column in a particular matrix is fixed; this is also true in a multidimensional array, in which the number of elements or *length* of each dimension is fixed.

Before providing a more formal definition of a multidimensional array, we must first define some related concepts:

- The data element type defines the elements within the array

- The shape defines dimensionality and the length of every dimension

- The index space defines the set of addresses of elements within an array

### Data element type

A data element type  $\mathbb{T}$  is a space from which the elements of a multidimensional array are chosen. Because we wish to represent multidimensional arrays on a computer,  $\mathbb{T}$  will usually contain a finite number of elements allowing every element of  $\mathbb{T}$  to be represented in a fixed number of bytes, which we will treat as the smallest addressable unit of storage.

T may also contain an *undefined* element, denoted  $\perp$ . When a multidimensional array is represented on a computer,  $\perp$  need not be a special value that may be distinguished from other data elements; it actually means that the element's value *is* undefined.

#### Shapes

A shape is a vector containing natural numbers. Letting

$$q \in \mathbb{N}$$

$$\mathbf{a} \in \mathbb{N}^q, \mathbf{a} = (a_0, \ldots, a_{q-1}),$$

a is a shape with dimensionality q, and

dimensionality of  $\mathbf{a} = \langle \mathbf{a} \rangle \stackrel{\triangle}{=} q$ .

If q = 0, a is represented by the empty set,  $\emptyset$ .

### Index space

Given a shape a with dimensionality q, the *index space* of a is defined:

$$\operatorname{index}(\mathbf{a}) \stackrel{\scriptscriptstyle{ riangle}}{=} \{(u_0, \dots, u_{q-1}) \in \mathbb{N}^q : 0 \le u_i < a_i\}.$$

If  $\mathbf{a} = \emptyset$  or some element  $a_i$  of  $\mathbf{a}$  is 0, we define

$$index(a) \stackrel{\triangle}{=} \{\emptyset\}.$$

Multidimensional array

Letting

$$q \in \mathbb{N}$$

TTO

$$\mathbf{a} \in \mathbb{N}^{q}, \mathbf{a} = (a_0, \dots, a_{q-1})$$

T be a set,

a multidimensional array A of shape a with data element type  $\mathbb T$  is a function

$$\mathbf{A}: \operatorname{index}(\mathbf{a}) \cup \{\bot\} \to \mathbb{T} \cup \{\bot\}.$$

A and a have the following properties:

| dimensionality of A | = | $\langle \mathbf{A} \rangle \stackrel{\scriptscriptstyle \Delta}{=} q$ | (2.1) |

|---------------------|---|------------------------------------------------------------------------|-------|

|---------------------|---|------------------------------------------------------------------------|-------|

shape of

$$\mathbf{A} = [\mathbf{A}] \stackrel{\mbox{\tiny $\square$}}{=} \mathbf{a}$$

(2.2)

size of

$$\mathbf{A} = |\mathbf{A}| \stackrel{\Delta}{=} |\operatorname{index}(\mathbf{a})|$$

(2.3)

length of dimension

$$i$$

of  $\mathbf{A} = [\mathbf{A}]_i \stackrel{\Delta}{=} a_i$  (2.4)

index space of

$$\mathbf{A} = \operatorname{index}(\mathbf{A}) \stackrel{\triangle}{=} \operatorname{index}(\mathbf{a})$$

(2.5)

$$\mathbf{A}(\perp) \stackrel{\Delta}{=} \perp$$

(2.6)

Note that in definition 2.3, unless q = 0 or an element  $a_i$  of a is zero, the size of A may be calculated

$|\mathbf{A}| = |\operatorname{index}(\mathbf{a})| = a_0 \times \ldots \times a_{q-1}.$

### Multidimensional spaces

The set of all multidimensional arrays, the *multidimensional array space*, is denoted M. Three subsets of M may be defined

arrays of shape

$$\mathbf{a} = \mathbb{M}_{\mathbf{a}} \stackrel{\triangle}{=} \{ \mathbf{A} \in \mathbb{M} : [\mathbf{A}] = \mathbf{a} \}$$

(2.7)

arrays of type  $\mathbb{T} = \mathbb{M}_{\mathbb{T}}$  (2.8)

$$\triangleq \{\mathbf{A} \in \mathbb{M} : \forall \mathbf{u} \in index([\mathbf{A}]), \mathbf{A}(\mathbf{u}) \in \mathbb{T}\}\$$

arrays of shape

$$\mathbf{a}$$

, type  $\mathbb{T} = \mathbb{M}_{\mathbf{a},\mathbb{T}} \stackrel{\scriptscriptstyle \Delta}{=} \mathbb{M}_{\mathbf{a}} \cap \mathbb{M}_{\mathbb{T}}$  (2.9)

# 10 CHAPTER 2. MULTIDIMENSIONAL SPACES AND DATA MAPPING

For example, let

$$a = (2, 3)$$

$$\mathbf{A}: \operatorname{index}(\mathbf{a}) \cup \{\bot\} \to \mathbb{R} \cup \{\bot\}$$

$$\mathbf{A}(r,c) = \text{element } (r,c) \text{ of the matrix } \begin{pmatrix} 0 & 1 & 2 \\ 3 & 4 & 5 \end{pmatrix}$$

More simply, we can write

$$\mathbf{A} = \left(\begin{array}{rrr} 0 & 1 & 2 \\ 3 & 4 & 5 \end{array}\right)$$

We can state the following properties of A:

$$A \in \mathbb{M}, A \in \mathbb{M}_{\mathbb{R}}, A \in \mathbb{M}_{\mathbf{a}}$$

$$\langle A \rangle = 2$$

$$[A] = (2,3)$$

$$[A]_0 = 2, \ [A]_1 = 3$$

$$index(A) = \{(0,0)(0,1)(0,2)(1,0)(1,1)(1,2)\}$$

$$|A| = 2 \times 3 = 6$$

$$A(1,0) = 3$$

$$A(\bot) = \bot .$$

# 2.1.2 Data and index mappings

Using the above definitions, functions may be defined between multidimensional arrays. For example, this function adds one to every element in a multidimensional array with shape a:

$$f: \mathbb{M}_{\mathbf{a},\mathbb{R}} \to \mathbb{M}_{\mathbf{a},\mathbb{R}}$$

$f(\mathbf{A})(\mathbf{u}) = \mathbf{A}(\mathbf{u}) + 1$  for all  $\mathbf{u} \in index(\mathbf{a})$ .

### 2.1. DEFINITIONS

#### Data mappings

A data mapping is a function between two multidimensional arrays with fixed (but not necessarily identical) sizes and of the same type  $\mathbb{T}$  which copies elements from the argument into the result.

Letting

$$p \in \mathbb{N}, \mathbf{a} \in \mathbb{N}^p$$

$$q \in \mathbb{N}, \mathbf{b} \in \mathbb{N}^q,$$

we define a data mapping f:

$$f: \mathbb{M}_{\mathbf{a}, \mathbb{T} \cup \{\bot\}} \to \mathbb{M}_{\mathbf{b}, \mathbb{T} \cup \{\bot\}}$$

$$f(\mathbf{A})(\mathbf{v}) = \left\{ \begin{array}{l} \mathbf{A}(\mathbf{u}) & \text{for some } \mathbf{u} \in \text{index}(\mathbf{a}) \\ \bot & \text{otherwise} \end{array} \right\} \text{ for all } \mathbf{v} \in \text{index}(\mathbf{b}).$$

#### Index mappings

Some data mappings may be expressed by defining an *index mapping* from one index space into another. Letting

$$p \in \mathbb{N}, \mathbf{a} \in \mathbb{N}^p$$

$q \in \mathbb{N}, \mathbf{b} \in \mathbb{N}^q$ ,

we define an index mapping g

$$g: index(\mathbf{b}) \cup \{\bot\} \to index(\mathbf{a}) \cup \{\bot\}.$$

From the index mapping g we may define a data mapping f:

$$f : \mathbb{M}_{\mathbf{a}, \mathbb{T} \cup \{\perp\}} \to \mathbb{M}_{\mathbf{b}, \mathbb{T} \cup \{\perp\}}$$

$f(\mathbf{A})(\mathbf{v}) = \mathbf{A}(g(\mathbf{v})) \text{ for all } \mathbf{v} \in \operatorname{index}(\mathbf{b}).$

It is necessary to define the mapping g 'backwards' to ensure that only one element of  $\mathbf{A}$  is mapped to each element of the result. A mapping that may be defined in this way is *data independent* because the correspondence between elements depends only on positions of data elements and not their values. Conversely, any data independent mapping may be defined by an index mapping. A *data dependent mapping* can map elements to different positions depending on the contents of the array being mapped. Letting

$a \in \mathbb{N}$ ,

an example of a data dependent mapping is a function which sorts real vectors of length a:

$$f: \mathbb{M}_{a,\mathbb{R}} \to \mathbb{M}_{a,\mathbb{R}}$$

$f(\mathbf{A}) =$ the elements of  $\mathbf{A}$  in sorted order for all  $\mathbf{A} \in \mathbb{M}_{a,\mathbb{R}}$ .

Letting

$$(a_0, a_1) \in \mathbb{N}$$

$\mathbf{a} = (a_0, a_1)$

$\mathbf{b} = (a_1, a_0),$

an example of a data independent mapping is an array transposition:

$$f: \mathbb{M}_{\mathbf{a},\mathbb{R}} \to \mathbb{M}_{\mathbf{b},\mathbb{R}}$$

$$f(\mathbf{A})(u_1, u_0) = \mathbf{A}(u_0, u_1)$$

for all  $(u_1, u_0) \in index(\mathbf{b})$ .

Expressed using an index mapping, the transposition example may be written:

$$g: index(\mathbf{b}) \cup \{\bot\} \to index(\mathbf{a}) \cup \{\bot\}$$

$$g(u_1, u_0) = (u_0, u_1) \text{ for all } (u_1, u_0) \in index(\mathbf{b})$$

$$f: \mathbb{M}_{\mathbf{a}, \mathbb{R}} \to \mathbb{M}_{\mathbf{b}, \mathbb{R}}$$

$f(\mathbf{A})(u_1, u_0) = \mathbf{A}(g(u_1, u_0)) = \mathbf{A}(u_0, u_1)$  for all  $(u_1, u_0) \in index(\mathbf{b})$ .

To simplify this notation,  $\perp$  will often not be included in data and index mappings; it may be assumed to be present unless stated otherwise.

### 2.1.3 Multidimensional data arrays

A multidimensional data array is a multidimensional array with some meaning attached to each of the dimensions. Whether a dimension represents time, spatial dimensions, temperature, frequency or any other quantity, it can be treated identically when it is represented as a dimension of a multidimensional array. Our description of a multidimensional data array is derived from the description of a KIPS *image* [66]; thus, the term *image* will often be used interchangeably with *multidimensional data array*.

A distinction can be made between *implicit* dimensions of the data, whose values are implicitly defined by their positions in the multidimensional data array, and *explicit* dimensions, whose values are explicitly specified as part of the array data type [66].

The same data set may be represented in several ways depending on whether each dimension is stored explicitly or implicitly. As an example, a data set representing the elevations of a two-dimensional grid of points on a landscape may be stored in several ways:

i. Two implicit dimensions representing spatial position (x, y) and one explicit dimension representing height z

### 2.1. DEFINITIONS

- ii. Three implicit dimensions, two of which represent spatial (x, y) position and one of which has a binary value representing the presence or absence of earth

- iii. One implicit dimension, representing nothing physical, and three explicit dimensions giving (x, y, z) values

Note that not all combinations may be used; it is usually not possible to represent a data set with an implicit height dimension z and explicit spatial dimensions (x, y) because of the requirement that each data element has the same size.

The representation used will depend on the use to which the data is put; representation (i) is the more usual, as the data is in a suitable form for many common image processing and visualization operations. Representation (ii) is necessary if the surface has any overhangs (i.e. the height field is not single-valued), and representation (iii) might be used if the surface were to be approximated by polygons.

The storage representation chosen also has an effect on quantization error, storage requirements and algorithmic efficiency. Quantization error is introduced into both the explicit and implicit representations. Implicit dimensions are quantized by the regular grid used to sample the data; this error may be reduced by sampling to a finer grid with a proportional cost in storage requirements and processing time. Explicit dimensions are quantized by a finite data type used to represent data elements; this error may be reduced by an approximately logarithmic cost in storage requirements and processing time. However, converting an implicit dimension to an explicit dimension may have great costs in both the need to explicitly represent all data values, and the greater algorithmic complexity in searching for particular data values.

### 2.1.4 Multidimensional devices

Devices may also be treated as multi-dimensional arrays.

We use the term *storage device* to refer to any device upon which data may be written and retrieved. Thus, a disk drive, a sequential computer's memory, machine readable display devices and distributed-memory parallel processing arrays are all examples of storage devices. We will use the term *memory* specifically for the fast random-access memory attached to processors.

Common examples of one-dimensional storage devices are disk files and a sequential computer's memory, where the elements are addressable by a single index.

Multi-dimensional devices are not yet so common. A distributed memory parallel computer can be regarded as a two-dimensional array, where the memory forms one dimension and the processor array one or more dimensions. A

### 14 CHAPTER 2. MULTIDIMENSIONAL SPACES AND DATA MAPPING

two-, or even three-, dimensional display can be regarded as multidimensional, and striped disks may be regarded as a very long and thin two-dimensional device, with a long axis being an address on disk and a short axis selecting the disk drive.

Disk files and sequential computers' memories also have some characteristics which are similar to distributed computers' memories which can in some circumstances make them behave as a two-dimensional storage device. Disk files are usually written as a series of *blocks*, where a block is the smallest unit of bytes that can be read or written at a time. Once a block has been read into a buffer, access to data in that block is very fast. This can make it appear as if the disk file has a two dimensional structure; access along the first dimension (inside the block) is very fast, and access along the second dimension (between blocks) is generally slower.

Similarly, most computers nowadays use *virtual memory*, which also segments memory into blocks. Access to blocks in physical memory is very fast, and access to blocks in secondary memory is slower. For computers with a fast data cache, a third level of access is added.

Although disk files and virtual memories do share some characteristics with multidimensional storage devices, there are many differences which limit the usefulness of the analogy; it is easy to find situations which cause poor performance in disk file access or virtual memory usage, but using these systems efficiently requires detailed knowledge about the underlying hardware and operating system.

The dimensionality of a distributed memory parallel processors is more evident and, unless programming in a parallel language which hides such things from the programmer, the dimensions are explicitly present in the programming language as memory references and communications operations.

In a multidimensional storage device, we will use the convention of numbering the dimensions in order of increasing access time. Usually, this will mean the memory dimension is device dimension zero. For the purposes of this thesis a memory array on a parallel device will be treated as if it were a data array, although there are physical restrictions which will affect the way data elements are accessed.

If a data array A is larger than the device array D we wish to map it onto, it will only be possible to map a subset of that data array onto the device. Usually we will assume that  $|A| \leq |D|$ , unless specified otherwise.

As an example, the smallest MasPar computer, the MasPar MP-1201-A, has 1024 processors, each with 16384 bytes of memory [4]. This could be treated as a multidimensional storage device with two dimensions, with the first dimension representing memory and containing 16384 elements, and the second dimension representing the processors and containing 1024 elements, giving a shape of [16384, 1024].

However, it is rarely possible or desirable to use all of a computer's memory

for storage of a single object. Specifying a smaller memory dimension allows many device arrays to be specified for the same physical device.

A MasPar can also be treated as a two-dimensional mesh computer. If our data array was 256 k-bytes or smaller, we could specify a device array with shape [256, 32, 32].

# 2.2 Data mapping on one-dimensional devices

When processing large multidimensional data sets on sequential computers and one-dimensional storage devices, the data mapping chosen can be important to the choice of algorithms and the efficiency of operations. Many data processing operations on these devices also require data remapping in the course of their execution. This section examines some current approaches to these issues.

### 2.2.1 The Multidimensional Tile Format

A method that allows flexibility in mapping multi-dimensional arrays onto a one-dimensional storage device, such as a disk file, is Fraser's *Multidimensional Tile Format* [29]. By hierarchically breaking down the image dimensions into a higher-dimensional space the tile format can describe many existing image storage formats, and allows scope for describing many more.

As well as providing flexibility in storage format specification, Fraser has derived efficient algorithms for reading and writing arbitrary blocks from a tile-format image file with only one pass over the file.

By streamlining the notation, adding some regularizing constructs, and including support for multidimensional devices, from the Multidimensional Tile Format we derived the parallel k-Tile format. A full description of the parallel k-Tile format is contained in section 3.1.

Some aspects of Fraser's work on the tile format have not been carried over to the k-Tile format, notably the application of the format to the storage of sparse data files.

### 2.2.2 Remapping algorithms and applications

When a data set is larger than the physical memory of a sequential computer, it is sometimes necessary to re-order the elements of the data set in a disk file to allow an image processing operation to be performed quickly. Even when an image will fit into the available memory, the properties of the algorithm may require the data to be remapped. Some examples of these operations are: scan-line operations [9, 31, 33, 44, 58, 61, 62, 71, 72], which require two- or three-dimensional images to be reflected and transposed about their axes; and different forms of the Fast Fourier Transform [8, 11, 15, 32, 35], which require

# 16 CHAPTER 2. MULTIDIMENSIONAL SPACES AND DATA MAPPING

multi-dimensional images to be transposed about their axes and their indices bit-reversed (chapter 7 examines these problems in more detail).

Several efficient algorithms for performing these operations have been used for many years, and all of them use, or are equivalent to, index-bit and indexdigit permutation algorithms. Fraser uses index-bit reversal techniques to allow images stored on disk or in an image display to be transposed or converted into a tiled format using only a small memory buffer [27, 28, 70]. Van Heel uses a mixed-radix perfect shuffle algorithm to perform transpositions of large multidimensional data sets using only small internal buffers, with the efficiency of the algorithm increasing with the size of the buffer [16, 30].

Many mapping and remapping techniques are *data dependent*, where the manner in which a pixel is stored depends upon its own values and those of its neighbours. Quad-trees and oct-trees [63], run-length encoding, numerical sorting and any form of data compression fall into this category. As we have limited the scope of this thesis to data-value independent mappings, we will not consider these further.

### 2.2.3 Hardware approaches to data mapping

Several hardware approaches have been taken to allow mapping-related tasks to be performed in hardware.

Lilleyman shows how the inclusion of a cross-bar switch between a microprocessor's address lines and its memory makes many implementations of the FFT more efficient by allowing data re-ordering to be performed in hardware with no movement of data between memory cells [45, 46].

Newman shows that with the use of a memory-management unit that pages data by tiles of a two-dimensional data array, rather than by rows (or parts of rows), the performance of many image-processing and graphics algorithms performed in a small physical memory can be greatly improved. The tiling is achieved by using the lowest-significant row- and column-bits within the data addresses to access data within a page, instead of the lowest-significant address bits. One example problem that began thrashing in 13 megabytes of RAM without tiling could be performed in an acceptable time using only two megabytes of tiled RAM [57].

Of course, either of these techniques could be simulated using software index bit permutation, but at a much greater cost in execution time and programming complexity.

## 2.3 Parallel architectures

There are a large number of parallel architectures available today, many of which have significantly varying characteristics. We outline some of these characteristics and then examine one parallel machine, the MasPar MP-1, in more detail. For the problems addressed in this thesis, the characteristics of the MasPar MP-1 are ideal [4]. We will also mention properties of two other parallel machines, Active Memory Technology's Distributed Array Processor (AMT DAP 500) [59] and Connection Machines Connection Machine 2 (CM-2) [37,67]; except for the algorithms, which are specifically for computers with characteristics similar to those of the MasPar, the specification techniques outlined in this thesis could be used with any computer architecture.

### 2.3.1 Properties of Parallel Architectures

### Instruction execution

Parallel machines may be divided into two classes, single instruction multiple data (SIMD) and multiple instruction multiple data (MIMD). SIMD machines contain many processors or processing elements (PEs), all executing the same instructions simultaneously; conditional execution and looping must be performed by temporarily disabling and enabling groups of PEs. The processors in MIMD machines are able to execute instructions independently, and each processor is more similar to that of a sequential machine. MIMD machines are sometimes used restrictively, with every processor executing the same program independently; this class of machine has been dubbed single program multiple data (SPMD).

In general a MIMD machine is at least as powerful as the corresponding SIMD machine with the same number of processors and same processing power within each processor, because the MIMD machine used in SPMD mode would perform at least as well as the SIMD machine. However, in terms of financial and physical cost, the SIMD concept has a number of advantages; because the instruction stream need only be decoded once, more processors can be built in a smaller space. Similarly, because the instruction stream need only be stored in one place, many megabytes of memory are saved. Many operations such as synchronization, memory operations and communication also benefit from central control [50].

These properties enable SIMD machines to achieve very high performance at a low cost for some classes of problems. Because of the regularity of the problems we have chosen to address in this thesis, SIMD machines are ideal for their solution.

### Memory addressing

Parallel machines may be further divided into two other classes, *shared memory* and *distributed memory* machines. In shared memory machines, every processor has access to the same address space. Because of the technical difficulty

### 18 CHAPTER 2. MULTIDIMENSIONAL SPACES AND DATA MAPPING

in allowing many processors to communicate with a single memory, parallel shared memory machines have only been implemented with a few processors. This in turn makes the MIMD paradigm more appropriate for shared memory machines.

In distributed memory machines, every processor has access to an individual memory space. This is technically easier to implement, but means that some form of inter-processor communication must be included in the architecture to allow data stored in different memories to be integrated.

Memory addressing in SIMD architectures comes in two forms: *direct* addressing and *indirect* addressing. With direct addressing, the address to be accessed is part of the instruction stream and hence is the same for every processor. In indirect addressing, the address to be accessed is generated from within each processor, and hence every processor may access data from a different address in its local memory.

Direct addressing is technically easier to achieve, both because addresses may be generated from outside the PEs and because the RAM hardware may be used more efficiently. However, the use of indirect addressing offers a number of advantages: Load-balancing may be improved by allowing each processor to proceed through a set of tasks in memory at a different rate [65]; parallel linked lists of different lengths and containing different elements may be implemented; and blocks of data may be moved by different offsets in every processor, which is very important in *scan-line algorithms* (see section 7.3.1).

#### Interprocessor communication

Some form of inter-processor communication is essential when dealing with distributed memory computers. There are trade-offs to be made between communication speed and flexibility, and consequently there are many solutions that have been used to solve the communications problem. We will mention three mechanisms for inter-processor communication among N processors: the 2d mesh, the hypercube and the crossbar switch. A thorough exploration of the properties of, and algorithms for, many communication networks is found in Leighton's book [43], and forms the basis for the following comments.